没了张屠户,就吃不了带毛猪?

作者:蜀山熊猫

来历:真视界

这些天看了不少讲国内EDA状况的帖子,有客观的也有极端离谱的,作为一名从业十余年的芯片规划工程师,我以一线从业者的视点来谈谈咱们在实践工作中的EDA软件运用状况究竟是怎样的吧。

先答复个很常见的问题:没有了美国的EDA,咱们是不是芯片都不能做了?这也是促进我写这篇文章的要素之一吧。

我的扼要答复是:180nm/350nm以上的部分老工艺线是可以用破解版或国产代替版持续做的,但深亚微米级130nm/90nm开端就很难离得开正版授权了,越往下越难,到了22nm以下,就完全不或许了。

和咱们熟知的office, autocad等东西类软件不一样,这种软件很朴实,脱机都可以用,完了打印出来就可以;芯片EDA东西软件的最大特点是它与芯片代工厂具有高度的绑定联系,由于咱们规划时,是需求代工厂供给数据包的,称之为PDK,包含了比方晶体管,MOS管,电阻电容等根底器材或反向器,与非门,或非门,锁存器,寄存器等逻辑单元的底子特征信息,这个数据包会不断优化,更新频频,一起对EDA软件有绑定及校验的效果,一般只支撑其时最新版的东西。

没软件,哥用手画不一样吗? 当年原子弹氢弹便是手算的呀。。

好的,首要我有必要要讲理解为啥有必要要运用自动化规划软件(EDA),不然我后边都是白说, 这部分懂的同学请直接往后拉,从第二部分开端看。文章有点长,受不了的请直接看第四段。

文章分五个部分:

一、为何需求用EDA;

二、EDA圈子的那些事;

三、不得不提的IP;

四、破局。

01 为何需求用EDA?

EDA,Electronic design automation,中文叫电子规划自动化。

最早的集成电路是用手艺做的,由于就几个管子,前端可以手艺完结其功用的核算,后端地图就依据电路图,将管子,连线用笔搬运为几何图形,画出胶带(算是掩膜的老祖宗),由于管子少,线也简略,所以不简略犯错。这是60年代——70年代中期的工作。(国内有些公司十年前都还在用,不知道现在怎样。)

可是,到了几十个,几百个器材或单元的时分就不可了,肉眼十分简略犯错。

比方这种:整个模块也就五百多个管子吧,截了大约5%的区域出来,这个人手艺怎样做呢,做完怎样确保百分百不会错呢,假如用自动布局布线东西,大约也就几秒就运转出来了,并且不会错。

数字网表导出来的电路图

这个自动布局布线出来的地图,用了7层金属,上千条毫无规矩的线,试问怎样去画?怎样去查?

数字地图

这是现在比较典型的一个SOC(system on chip)芯片(CPU便是SOC的一种)的图,里面包含了数字电路也包含了模仿电路IP,上面这个数字地图的截图,或许仅仅下面这个完好地图的千分之一,甚至更少,你要知道最陈旧的SOC里的晶体管都是千万级以上,现在的个数更是动辄便是几亿,甚至上十亿:

典型的SOC暗示图

一条线连错了,或许整个产品的功用就变了,也便是你花几千万,只能得到一堆人都砸不了的板砖。之前一切投入悉数打水漂。一般来说制程越先进,制作和研制费用愈来愈贵重,哪怕是很老的0.5um, 0.35um的工艺,尽管只需几十万,几百万,但那也是钱哪,更甭说到了28nm下制程动辄都是千万级美元的费用,10nm,7nm更是亿级美元了,流几回片没成功直接关闭的公司不计其数。所以有必要运用核算机来辅佐规划!

02 EDA圈子的那些事

【1】EDA的挑选

做了张脑图,咱们先看下芯片的大致流程:

当然实践规划中会更为杂乱,并跟着制程的变小,会进一步加重流程各环节的杂乱度以及添加环节内部的新的验证项目,但大体仍是以下过程:前端规划和仿真——后端规划及验证——后仿真——signoff查看——数据交给代工厂(以gds的方式)

略微解释一下几个重要概念:

Signoff, 中文翻译叫签核,比较笼统,简略说便是按厂家的默认设置要求做最终一次的规矩验证,一般咱们在规划的时分,会将厂家要求的规范进步一些来做。

后端规划:可以理解为将电路从器材符号方式转为几何图形方式,以辅导掩膜版的规划。

然后,我把规划流程里各个环节能用且好用的软件列一下(可以正常的看到底子都是Cadence, Synopsys, Mentor三家的产品):

模仿及混合信号类(包含模仿前端规划及仿真,模仿后端规划及验证,芯片后仿真):

电路及地图规划东西:Virtuoso (Cadence), 0.18um,0.35um等老工艺可以用L-edit.(这个不受限)

地图物理验证东西:Calibre(Mentor),老工艺还能用Assura(Cadence),dracura(Cadence,更老,十几年前刚结业那会儿用过)

地图参数提取东西:Star-RC(synopsys), Calibre XRC(Mentor),QRC(Cadence)

电路仿真东西:Hspice(Synopsys) ,Spectre(Cadence), ALPS(华大九霄,我国)

数字及SOC类(数字前端,数字后端,验证,仿真):

RTL归纳东西 :DC(Design compiler,Synopsys)

仿真验证东西:VCS(Synopsys), ModelSim(Mentor),Incisive,Indago, MDV,VIP(Cadence)

数字后端规划东西:ICC(Synopsys),Innovus/Encounter(Cadence) 还有180nm制程可用的老掉牙的Astro( synopsys).

DFT东西:DFT Compiler (Synopsys)

物理验证东西:ICV(Synopsys)PVS(Cadence), Calibre(Mentor)

signoff 时序/噪声/功耗剖析东西:Prime time, PT(synopsys),PrimeRail(Synopsys) ,redhawk Fusion(Synopsys, 这套flow产品的中心redhawk是ansys的产品,ansys为s家战略协作),Totem(Ansys, 美国)

PCB:

Allegro(Cadence) :这个还好,不更新也没太大个问题。

这儿再简略说下国内的EDA状况,反向提图抄袭软件其实是走在国际前列的,芯X景(听说还要上市圈钱),客户除了早就被拉黑的外,都不敢说用了他家产品,怕吃官司,这种不值得发起,由于他们干的事早已超出了他们所声称的只用于合理学习的底线;

正向规划里现在真实得到认可的只要华大九霄(我为他们点个赞),但首要是模仿产品上,详细的说是模仿电路的仿真东西(ALPS),再细化下是电源类产品的仿真上,有他们的独特及NB之处,他们也有对标 virtuoso的兼容性产品Aether,可是得在老练工艺下用。国内的EDA仍然处于一个辅佐人物状况,还有很长很长的路要走。

可以这么说,国际上一切的芯片规划公司,不论你是5nm仍是350nm吧,不管你多NB,多逆天,必定选用了这三家的至少一种软件,哪怕是盗版 。

【1】规划渠道化产品闭环

Synopsys和Cadence一向的开展战略是渠道性开展,也便是说并不是某个环节的规划软件强,而是从前端规划-前仿真/验证-后端规划-后端验证仿真直到流片的整套产品都很强,并构成规划的闭环,比方synopsys的Milkway, Cadence的OA(OpenAccess)。

大略的说,模仿/数模混合芯片规划用cadence渠道,数字芯片规划选用synopsys渠道,当然实践并非如此肯定,有必定的穿插运用状况。

关于客户来讲,他们天然会倾向于渠道化的EDA的收买,而不是分门别类的买,由于省劲就从另一方面代表着省钱啊,除非你的某项产品极端NB,比方Mentor的功用或物理验证产品,Ansys家的功耗剖析软件,那的确凶猛,尤其是物理验证C,S两家真干不过,现已是全球一切代工厂公认的金规范,也迫于独占压力收不了,那只能战略协作。

1)与工艺厂的绑缚 (EDA联盟+IP联盟)

然后呢,EDA的独占还表现在于工艺厂的绑缚上,工艺厂前期要进行工艺研制,必然也要进行器材,简略功用芯片的规划,要规划就得根据eda规划渠道支撑,这时分Synopsys, Cadence等EDA公司就来送温暖了,他们甚至会免费直接帮你规划多种根底IP, 各种规划的功用IP以扩大你的IP库,IP库越大越全,对客户的吸引力也就越大,win-win;

在功用验证,物理验证环节,则有Mentor的一席之地,物理验证会贯穿并频频往复于后端规划的全流程,关于软件的功率和可视化要求很高,这点calibre做得十分好。别的EDA供货商还会给校园客户优惠价甚至免费,其意图也很明显,培育用户习气,除非校园也是荣耀的上了美帝黑名单。

也便是:EDA 东西+IP授权的绑缚。

这样一整,进入投产阶段后,工艺厂发给客户的PDK规划包天然也只能支撑 Synopsys, Cadence,Mentor的了,其他的EDA代替品,多在兼容性上做功,并且无法供给渠道化产品,加上兼容和原生,在时效及运用上都有很大的差异。

一旦做强了还面临着Cadence,Synopsys的收买/绞杀要挟。仍是那句话,人家供给的是渠道,除非你能像Mentor那样供给整套验证渠道也可。

03 不得不提的 IP

EDA说完了,再说说IP,IP关于今日SOC规划的重要性不必赘述了, Synopsys, Cadence的另一个杀手锏级的独占产品:接口类IP,这是每一颗SOC必不可少的东西,比方:高速SerDes, ethernet以太网,PCIE, CPRI, SATA,USB,Type-C,MIPI, HDMI,DP...还有DDR; 如下图所示,Synopsys 的IP事务在总营收里占第二。

Synopsys 2013~2018的产品及服务的营收占比

形似从65nm开端吧,每一代工艺出来的前期底子只要Synopsys和Cadence两家可选,由于这两家是先进工艺研制的唯二工艺-产品的规划及验证渠道,他们老早就进去了,至少是从规划PDK(芯片规划东西包)开端,产线敞开后,连续才会有其他IP供货商或自主研制的接口产品可用, 但到了14nm开端,除S,C两家外,很长时刻底子只要rambus, aphawave,esilicon等公司的IP可用,rambus,esilicon是美国公司,alphawave是加拿大公司,加拿大你懂的,不过华为是他们的T1客户。。。

可是7nm,5nm下,能做到一切类型的接口IP都供给的,仍是只要Synopsys或Cadence。就在前天,Cadence发了款TSMC 7nm的超高速112G/56G 长距离SerDes,用于云数据中心和光网络芯片,5G根底设施的中心IP。SMIC14nm的10G多协议PHY IP也是他们独家的,5月14日发布的。

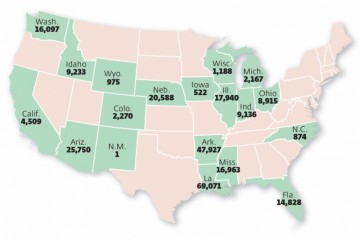

然后我来一张2019年半导体IP厂商TOP10榜单:

榜单中前三个就不说了:

SST:得益于NVM接口的盛行,直接从十名开外, 冲到了第三。(总部美国加州)

imagination(一家被中资布景的美国私募操控的英国公司。。??) ,其首要产品是GPU IP,国有化了,但这两年垮得很凶猛;

Ceva(以色列) 首要是DSP;

Verisilicon(芯原,要点提一下,这家首要研制力气在我国,外面名望不大,但业界名望很大,很NB,作为研制力气首要在我国的公司,海外营收居然占了70%+ ,不乏谷歌,Facebook、博世、亚马逊、英特尔、恩智浦,高通,华为这样的巨子客户。

全球IP供货商排名里排第7,国家大基金和小米这两年都投了他们,昨日科创板上市已通过会了,是家我国公司。他们尽管技能储备不错,但体量偏小并且研制投入占比极大,所以财报不太美观,后边看本钱注入后,有进一步扩张并做大的时机,看好他们厚积薄发。

他们的重要布局是Globalfoudry, Samsung 22nm FDSOI产线的低功耗产品,是三星和GF的IP联盟中的战略协作伙伴。

Achronix(美国), 首要是FPGA;

eMemory,看姓名就知道memory。

04 破局

下策:用盗版EDA。国内有公司这么干,省钱是一方面,首要仍是由于上了黑名单,人家给钱也不卖,用盗版软件规划好,然后交给第三方署理公司处理,投片,然后交给厂家代工,可是这底子只能在0.18um甚至更高的制程的产品,65nm以下的产品底子上很难。(现在这种署理公司越来越少了,黑名单都快拉满了。)

我就不说这玩意儿不能破解了,我信任这国际上没有肯定无懈可击的防护系统,哪怕这几家的物理license manager系统规划简直现已做到了国际最好。

底子原因仍是我刚刚说的工艺厂和EDA利益绑定的问题,工艺厂的规划数据包(PDK),尤其是验证文件的更新十分频频,尤其是新工艺,由于跟着各种测验片,量产版的测验反应,会不断的调整器材模型,规划规矩,不断迭代,让良率到达最高,一个月一更的都见过,甚至是1.x版别直接升到2.x版,都不是0.0x这么细小迭代。这种起伏的更新让规划重来的都有。

几个尖端代工厂的东西底子都是用最新版别,所以放出来的更新PDK也是用最新版东西校验, 你老的东西很或许就得跟着更新,盗版底子来不及,也没什么人乐意干这种费力不讨好的事,所以能找到盗版的简直都是老点的版别。除非是老工艺,比方台积电的0.18um,形似七八年没更新了,由于现已完美了,就不存在过期这种问题。

比方说之前做28nm以下模仿规划,最早还能用virtuoso的ic6.16, 6.17,到后来成了ICADV122,直到现在只能用ICADV123, 验证就更快了,一年一代.比方这个Mentor 的Calibre,一年一个大更新,里面还有小更新,17年的是打不开19年的东西校验过的数据的,一个版别对应一批License(按个数卖):

Mentor Calibre版别暗示

这也是为啥license一般都是买短期的,也可以称之为租借,终身买断的那是家里有钻石矿的。

假如对你中止了技能上的支撑,那么也就从另一方面代表着更新中止,License没停你老的可以接着用。当年中兴被封杀时,网上泄显露的Cadence群发邮件也提到过,可是实践上,我了解到的华为被制裁的没中兴那么惨,中兴其时是直接一刀下去的。而华为不是,由于美国想拿这事作为重要的商洽筹码,而不是直接销毁筹码,停止商洽。

最终,你盗版规划好的数据,为什么得拿给第三方润一下(润笔费可不菲。),也是由于数据在制版前,工艺厂还会校验,由于license是与公司物理称号及专用license服务器网卡地址悉数绑定的,数据来历不明的不会给你流片的。

有人说,那咱们自己的工艺线呢,悄悄的不可嘛?芯片工业是个开展了几十年的全球化的链条,所谓的3+2结构,一家做不完全部环节。各种布景的人凑一堆玩一个游戏,最考究的便是一个游戏规矩,哪怕这个规矩有问题,可是绝大多数的人乐意信任就没问题,比方常见的便是不能把客户数据偷去自己出产自己卖,或卖给其他公司;

保护IP及东西联盟的利益,不接来历不明的单;一旦有人损坏规矩,就会被全联盟抵抗甚至出局。(就好比咱们在玩我国象棋,你非得说悔棋可以或要用国际象棋的规矩来玩。)

芯片3+2结构

中策上策:先打部分战争,不要一来就想整个大的,树立一个独有的系统,逆全球化是逆势而为,是特没谱才干的事。某国越关闭,咱们就越敞开,让自己在全球系统有自己的方位,哪怕一开端微乎其微。

扶持本乡EDA的开展,但需求很长的路要走,技能壁垒,专利壁垒这种东西并不是砸钱就可以破掉的,华人工程师在美国本乡被防得很死,尤其是在中心技能上;并且EDA这个职业很烧钱,未来报答远远比不上互联网职业,其总的市场规划也就100亿美元,这个只能靠扶持。

别的,我再说一次,反向抄袭软件不在评论之列,这种流氓盗版公司请让他死掉,他们是导致芯片职业恶性及下作竞赛的推手(这些年因被抄袭而死掉的不少是国内的有技能有立异的草创公司),这是我的一向观念。

可是,咱们没必要一来就以完全取代为意图,可以从部分打破,把某一类东西做到极致,比方现在华大九霄的模仿产品仿真东西便是一个很好的打破口,想Ansys那样,成为工艺厂的金规范,人家想踢你都踢不掉,客户不容许啊。

EDA-IP-工艺厂需求协同开展,各司其职,让专业的人做自己最拿手的事,防止恶性竞赛,才是功率最高的战略。在EDA还没起步的时分,就先为现有的能在国际上排上号的IP公司和代工厂,促进IP联盟,然后再带动EDA的开展。

有人说讲这些有啥用,是让咱们认命,认怂,听天由命的意思吗?当然不是。

怎样去应对危机?1.认清自己的优势和底线,去坚持它;2.认清自己的下风与缺乏,去补偿它去纠正它或许暂时去绕过它。这才是面临危机时正确的处理方式,而不是一味的头脑发热要打要杀以及直接认输下跪,那都是莽夫和胆小鬼的行为。

剖析局势有利于认清局势,认清了局势可以在必定程度上协助勇者更好的知难而进,寻求到务实而有用的包围办法,而不是盲意图如大炼钢铁般的劳民伤财,胡搅胡来。信任不管革命先烈的长征成功,仍是两弹一星重大打破,甚至改革敞开的巨大成就,这都不是脱离现实,只靠空喊标语,一腔热血得到的。掩耳盗铃才是最可耻的认输。